This eliminates simple bias, and is easy to implement. It thus represents a falling edge with a 1, and a rising edge with a 0. It considers successive pairs of consecutive, non-overlapping bits from the input stream, taking one of three actions: when two successive bits are equal, they are discarded a sequence of 1,0 becomes a 1 and a sequence of 0,1 becomes a 0. John von Neumann invented a simple algorithm to fix simple bias, and reduce correlation.

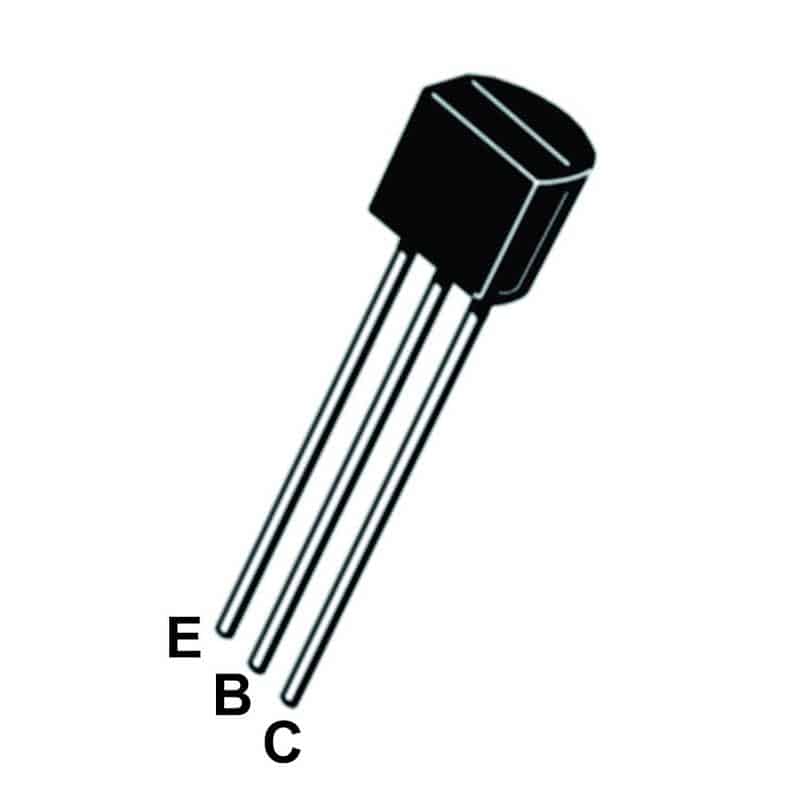

2N2222A TRANSISTOR SAMPLES GENERATOR

He ran a simple program to read two independently generated output streams from the HRNG and produce a third stream, as outlined by the following (from Random Sequence Generator based on Chua Circuit ) This delay has been set to 500?s, producing a 2000bit/s stream.

2N2222A TRANSISTOR SAMPLES SOFTWARE

On the software side I have basically used the same code I had written for the Chua random generator: at the beginning GPIO4 is configured as input, then one bit is read (and its value is optionally printed), next we wait for a delay and repeat. Of course I'm going to assume that the bit-stream still contain bias and correlation, so a de-skewing technique for reducing bias and correlation will be used anyway. This time there is no need to minimize bias inherent in the operation of the generator, if all went well we should get a probability of 1s and 0s very close to 50%. The original author of the circuit the OP is using believed that a relatively even balance between 0's and 1's produce a non-biased output (it doesn't), but they didn't appear to actually test that asuumption since they used 'whitening' techniques from the start: Also, he used a digital input to generate "1"s and "0"s - your use of the ADC throws in an additional complication. Your circuit has no provision for adjustments and can't produce a zero mean signal. Trying to design a circuit that could produce a symmetrical, zero-average noise signal from a reverse biased p-n junction in avalanche breakdownīut it really isn't clear how he achieved and verified the output of the hardware other than with software. The author of the HRNG link you posted claims to have gone to some effort to reach his goal, namely The 'best' current for maximum noise varies with the device however, the ones I have tested have generally been 5-50 uA.įurther, there have been several people who have tested a variety of such transistors, and the 2N3904 tend to produce the most noise. Further the reverse bias transistor used in the OP example doesn't enter the breakdown zone until about 8-9V, though I have found a few examples of the 2N3904 (the transistor typically specified) that entered breakdown at lower voltages, the mean tends to be around 9V, with noise peaking near 12V. we are talking nanocurrents here, any help you can get to boost the starting point is a bonus.I rebiased the zener to get the exact datasheet current point for peak noise and it burst into life.Īlbeit with the nyquist sample rate problem, so im not cel3brating yet, just my 2c that 5v circuits can be made noisy with a bit of care,a datasheet and a calculatorĪvalanche noise is generally an order of magnitude lower for 5V and below sources (typically zeners') when compared to 12V+ sources, even when current is adjusted for.

i guess most mfrs try to reruce noise and though zeners are inherently noisy there is a point on their curve where they are most noisy. it didnt work.until I realised that the key point is the current through the noise source is quite critical. I dropped it to 5v, changed the NPN bias to get 2.5 ish midpoint and enough gain to exceed the upper and lower hystersis points of the 393. my original circuit was stolen from a 12v design.

Just to reinforce what Coding Badly pointed out, I made a circuit based on that type of design using 2n2222 and I found that a supply of 5V and 9V didn't work well.

0 kommentar(er)

0 kommentar(er)